22: Digitaltechnik und Entwurfsverfahren, Vorlesung, SS 2017, 18.07.2017

Author

Editor

Participating institute

Institut für Anthropomatik und Robotik (IAR)

Genre

Description

- 0:00:00 Starten

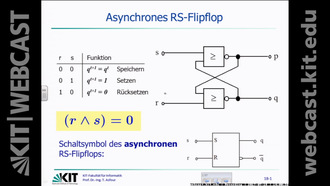

- 0:00:18 RS-Flipflop

- 0:03:18 Pegelgesteuertes RS-Latch

- 0:06:17 D-Latch

- 0:08:36 Taktflankengesteuertes D-Flipflop

- 0:11:20 Einflankengesteuertes D-Flipflop

- 0:13:48 Nebenbetrachtung

- 0:18:45 D-Flipflops

- 0:20:45 Zur Erinnerung

- 0:22:15 Schaltwerke mit D-Flipflop

- 0:24:17 Schaltwerke mit D-Latches

- 0:27:42 Zusatzbetrachtung für flankengesteuerte Flipflops

- 0:30:01 Setzeit (Setup-) und Haltezeit (Hold-Time)

- 0:32:10 Zweiflankengesteuerte Flipflops

- 0:34:43 Zweiflankengesteuertes D-Flipflop

- 0:40:58 JK-Flipflop

- 0:51:13 Ansteuertabelle

- 0:56:51 Beispiel: Asynchron rücksetzbares JK-Flipflop

- 1:01:21 T-Flipflop

- 1:03:27 T-Flipflop: Ansteuertabelle

- 1:04:04 Zusammenfassung Flipflops

- 1:06:54 Entwurf synchroner Schaltwerke

- 1:08:20 Serienaddierer

- 1:12:08 Blockschaltbild des Serienaddierers

- 1:12:55 Automatengraph

- 1:17:00 Wahl der Zustandskodierung

- 1:17:58 Zustandskodierung beim Serienaddierer

- 1:18:53 Kodierte Ablauftabelle

- 1:22:33 Anmerkungen

- 1:23:42 Ansteuerung des Flipflops

- 1:25:04 Minimierte Ausgangs- und Ansteuernetze

- 1:26:49 Realisierung des Serienaddierers

Duration (hh:mm:ss)

01:29:12

Series

Digitaltechnik und Entwurfsverfahren, Vorlesung, SS 2017

Published on

27.07.2017

Subject area

License

| Resolution | 1280 x 720 Pixel |

| Aspect ratio | 16:9 |

| Audio bitrate | 97009 bps |

| Audio channels | 2 |

| Audio Codec | aac |

| Audio Sample Rate | 48000 Hz |

| Total Bitrate | 902880 bps |

| Color Space | yuv420p |

| Container | mov,mp4,m4a,3gp,3g2,mj2 |

| Media Type | video/mp4 |

| Duration | 5352 s |

| Filename | DIVA-2017-449_hd.mp4 |

| File Size | 4.096 byte |

| Frame Rate | 25 |

| Video Bitrate | 799776 bps |

| Video Codec | h264 |

Media URL

Embed Code

Digitaltechnik und Entwurfsverfahren, Vorlesung, SS 2017

Episodes 1-26

of 26