FAQ

Audio-/Videodatei publizieren

Digitaltechnik und Entwurfsverfahren, WS 2015/2016, gehalten am 18.01.2016, Vorlesung 18

Autor

Beteiligtes Institut

Institut für Anthropomatik und Robotik (IAR)

Genre

Beschreibung

- 0:00:00 Starten

- 0:00:10 Kapitel 4.2 Entwurf asynchroner Schaltwerke

- 0:00:35 Einleitung

- 0:00:44 Beispiel: Einfacher Speicher

- 0:01:44 Kapitel 4.2.1 Aufstellen des Automatengraphen

- 0:01:51 Vorgehensweise

- 0:02:17 Automatengraph des einfachen Speichers

- 0:04:25 Funktionsweise

- 0:05:17 Kapitel 4.2.2 Aufstellen der Automatentafel

- 0:05:28 Übertragen des Automatengraphen in die Automatentafel

- 0:06:54 Stabilitätskriterium

- 0:08:07 Beispiel: Flussmatrix des einfachen Speichers

- 0:08:45 Mögliche Formen eines Zustandsübergangs (1)

- 0:10:44 Mögliche Formen eines Zusatndsübergangs (2)

- 0:11:18 Kapitel 4.2.3 Wahl der Zustandskodierung

- 0:11:37 Binäre Zustandskodierung

- 0:12:54 Anzahl der Zustandsvariablen

- 0:14:03 Wahl geeigneter Zusatndskodierung

- 0:15:08 Übergang 1

- 0:16:39 Mögliche Fälle eines Wettlaufs (1)

- 0:17:37 Mögliche Fälle eines Wettlaufs (2)

- 0:18:53 Kritischer Wettlauf

- 0:19:36 Wettlauffreie Zustandskodierung

- 0:20:48 Anmerkungen

- 0:21:17 Beispiel: Einfachen Speicher

- 0:22:02 Kapitel 4.2.4 Erzeugen der Ausgabe- und Übergangsschaltnetze

- 0:22:15 Erregungsmatrix

- 0:23:17 Ausgabe- und Übergangsschaltnetze (1)

- 0:24:47 Ausgabe- und Übergangsschaltnetze (2)

- 0:26:22 Schaltbild des Speichers

- 0:27:41 Das asynchrone RS-Flipflop (1)

- 0:29:08 Das asynchrone RS-Flipflop (2)

- 0:29:44 Probleme asynchroner Schaltwerke (1)

- 0:30:26 Probleme asynchroner Schaltwerke (2)

- 0:31:07 Probleme asynchroner Schaltwerke (3)

- 0:31:36 Kapitel 4.2.5 Analyse asynchroner Schaltwerke

- 0:31:47 Einleitung

- 0:31:57 Analyse asynchroner Schaltwerke (1)

- 0:33:40 Analyse asynchroner Schaltwerke (2)

- 0:34:41 Analyse asynchroner Schaltwerke (3)

- 0:35:10 Analyse asynchroner Schaltwerke (4)

- 0:37:19 Analyse asynchroner Schaltwerke (5)

- 0:40:05 Analyse asynchroner Schaltwerke (6)

- 0:41:35 Analyse asynchroner Schaltwerke (7)

- 0:42:44 Analyse asynchroner Schaltwerke (8)

- 0:43:40 Analyse asynchroner Schaltwerke (9)

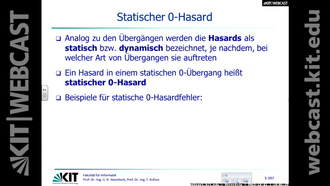

- 0:44:01 Genauere Analyse eines Übergangs (1)

- 0:46:15 Genauere Analyse eines Übergangs (2)

- 0:48:18 Verhalten des Flipflops bei Auftreten des Hasardfehlers (1)

- 0:54:06 Verhalten des Flipflops bei Auftreten des Hasardfehlers (2)

- 0:55:35 Verhalten des Flipflops bei Auftreten des Hasardfehlers (3)

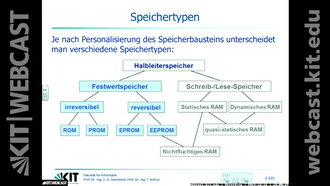

- 0:56:14 Kapitel 4.3 Flipflops als Zustandsspeicher

- 0:56:48 Einleitung

- 0:57:46 Kapitel 4.3.1 RS-Flipflop

- 0:57:56 Asynchrones RS-Flipflop

- 0:58:35 Verhalten des RS-Flipflops

- 0:58:45 Pegelgesteuertes RS-Latch

- 0:59:39 Anmerkung zur Notation

- 1:00:37 Ansteuertabelle (RS-Flipflop) (1)

- 1:01:09 Herleitung der Ansteuertabelle

- 1:02:59 Ansteuertabelle (RS-Flipflop) (2)

- 1:03:49 Kapitel 4.3.2 D-Flipflop

- 1:04:00 D-Latch (1)

- 1:05:57 D-Latch (2)

- 1:07:01 Ansteuertabelle des D-Latch

- 1:07:48 Pegelgesteuertes synchrones D-Flipflop

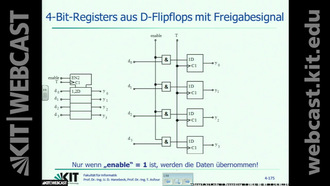

- 1:09:07 Taktflankengesteuertes D-Flipflop (1)

- 1:10:23 Taktflankengesteuertes D-Flipflop (2)

Laufzeit (hh:mm:ss)

01:10:50

Serie

Digitaltechnik und Entwurfsverfahren, WS 2015/2016

Publiziert am

26.01.2016

Fachgebiet

Lizenz

Aufrufe

117

| Auflösung | 1280 x 720 Pixel |

| Seitenverhältnis | 16:9 |

| Audiobitrate | 105093 bps |

| Audio Kanäle | 2 |

| Audio Codec | aac |

| Audio Abtastrate | 48000 Hz |

| Gesamtbitrate | 911104 bps |

| Farbraum | yuv420p |

| Container | mov,mp4,m4a,3gp,3g2,mj2 |

| Medientyp | video/mp4 |

| Dauer | 4250 s |

| Dateiname | DIVA-2016-118_hd.mp4 |

| Dateigröße | 4.096 byte |

| Bildwiederholfrequenz | 25 |

| Videobitrate | 799911 bps |

| Video Codec | h264 |

Mediathek-URL

Embed-Code

Digitaltechnik und Entwurfsverfahren, WS 2015/2016

Folgen 1-23

von 23