FAQ

Audio-/Videodatei publizieren

Digitaltechnik und Entwurfsverfahren, WS 2015/2016, gehalten am 25.01.2016, Vorlesung 20

Autor

Beteiligtes Institut

Institut für Anthropomatik und Robotik (IAR)

Genre

Beschreibung

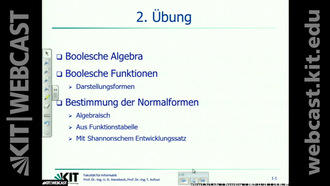

- 0:00:00 Starten

- 0:00:10 Kapitel 4.4.5: Beispiel: Folgenerkenner

- 0:00:22 Verbale Aufgabenstellung

- 0:01:52 Technische Randbedingungen

- 0:02:15 Formalisierung der Aufgabe

- 0:04:56 Automatengraph

- 0:05:48 Automatentabelle

- 0:07:06 Zustandskodierung

- 0:07:47 Kodierte Ablauftabelle

- 0:10:22 Ansteuerfunktionen der Flipflops

- 0:11:41 Ausgabefunktion

- 0:11:54 Realisierung des Schaltwerks mit den gegebenen Bauelementen

- 0:12:53 Kapitel 4.5: Spezielle Schaltwerkbausteine

- 0:13:16 Einleitung

- 0:13:36 Kapitel 4.5.1: Register

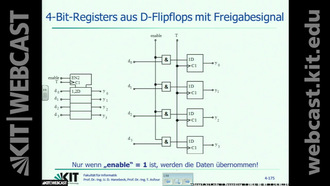

- 0:14:35 4-Bit-Registers aus D-Flipflops mit Freigabesignal

- 0:15:22 Kapitel 4.5.2: Schieberegister

- 0:16:48 Serien-Parallelwandlung

- 0:17:25 Schieberegister

- 0:17:41 Schieberregister mit parallelen Eingängen

- 0:18:13 Schieberegister: Division/Multiplikation mit 2

- 0:19:17 Schieberegister: Umlaufspeicher/Ringzähler

- 0:19:44 Konkreter Baustein: 74LS194

- 0:20:07 Funktionsmodi des 74LS194

- 0:20:38 Betriebsarten des Schieberegisters

- 0:21:06 Kapitel 4.5.3: Zähler

- 0:21:27 Aufgaben in digitalen Systemen

- 0:22:14 Grundlegendes Übergangsdiagramm

- 0:22:42 Anmerkungen

- 0:23:12 Schaltsymbole

- 0:23:50 Beispiel: Synchroner 3-stelliger Duahlzähler

- 0:29:58 Herleitung

- 0:37:13 Asynchrone Zähler (Ripple Counter)

- 0:41:58 Nachteile asynchrone Zähler

- 0:42:46 Partitionieren

- 0:44:21 Kapitel 4.5.4: Programmierbare Bausteine

- 0:44:35 Einleitung

- 0:45:05 NAND-Gatter im Gate-Array-Entwurfsstil

- 0:46:04 Aufbau eines MPGA (ASIC)

- 0:46:27 MPGA & ASIC: Vor- und Nachteile

- 0:46:59 Prinzipieller Aufbau eines FPGAs

- 0:48:00 Aufbau eines FPGA-Bausteins

- 0:48:18 Xilinex Virtex FPGA Model

- 0:48:37 CLB (Configurable Logic Block) eines XILINX Virtex-FPGAs

- 0:48:42 FPGAs und MPGAs

- 0:49:19 FPGAs

- 0:49:30 Der Entwurfsprozeß mit FPGAs

- 0:50:00 Entwurf mit FPGAs

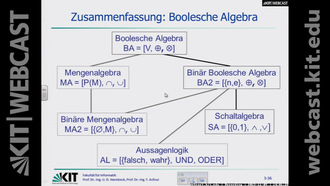

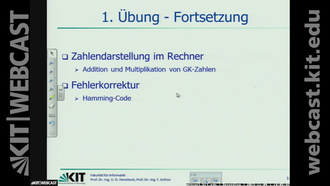

- 0:50:54 Kapitel 5: Rechnerarithmetik

- 0:51:46 Einleitung

- 0:52:04 Kapitel 5.1: Addition und Subtraktion

- 0:52:41 Addition von Festkomma-Dualzahlen

- 0:53:15 Addition von Gleitkommazahlen

- 0:53:30 Kapitel 5.1.1: Voll- und Halbaddierer

- 0:53:33 Halbaddierer

- 0:54:57 Volladdierer

- 0:57:27 Schaltnetz und Schaltsymbol

- 1:00:11 Serielle Addition (Papier- und Bleistift-Methode)

Laufzeit (hh:mm:ss)

01:01:41

Serie

Digitaltechnik und Entwurfsverfahren, WS 2015/2016

Publiziert am

01.02.2016

Fachgebiet

Lizenz

Aufrufe

135

| Auflösung | 1280 x 720 Pixel |

| Seitenverhältnis | 16:9 |

| Audiobitrate | 107895 bps |

| Audio Kanäle | 2 |

| Audio Codec | aac |

| Audio Abtastrate | 48000 Hz |

| Gesamtbitrate | 913845 bps |

| Farbraum | yuv420p |

| Container | mov,mp4,m4a,3gp,3g2,mj2 |

| Medientyp | video/mp4 |

| Dauer | 3701 s |

| Dateiname | DIVA-2016-133_hd.mp4 |

| Dateigröße | 4.096 byte |

| Bildwiederholfrequenz | 25 |

| Videobitrate | 799853 bps |

| Video Codec | h264 |

Mediathek-URL

Embed-Code

Digitaltechnik und Entwurfsverfahren, WS 2015/2016

Folgen 1-23

von 23