FAQ

Audio-/Videodatei publizieren

Rechnerorganisation, SS 2015, gehalten am 02.06.2015, Vorlesung 13

Autor

Beteiligtes Institut

Institut für Technische Informatik (ITEC)

Genre

Beschreibung

- 00:00:10 5.3 RISC & CISC

- 00:05:50 Programmiermodell: Intel 80x86

- 00:07:55 Befehlsaufbau der Intel-x-86 Prozessoren

- 00:08:11 CISC & RISC

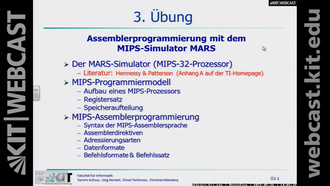

- 00:08:54 Mima-Architektur (Übungsblatt 3)

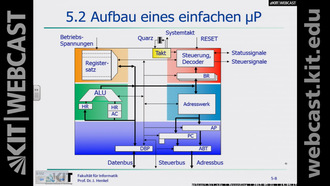

- 00:09:04 Mikroprogrammsteuerwerke

- 00:13:12 Implementierung des Steuerwerks

- 00:13:34 Mikroprogrammierung

- 00:18:26 CISC (complex instruction set computers)

- 00:23:16 Limitationen der CISC Architekturen

- 00:30:48 Prozentualer Anteil von Anweisungen in Hochsprachenprogrammen

- 00:31:15 RISC (reduced instruction set computers)

- 00:35:01 Zielvorstellungen für RISC-Rechner

- 00:35:10 RISC-Rechner aus heutiger Sicht

- 00:35:15 RISC & CISC

- 00:35:58 Aufbau eines RISC-Prozessors

- 00:37:44 RISC - superskalar

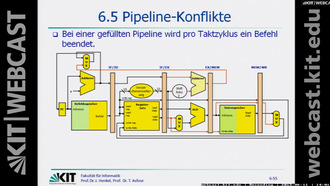

- 00:43:36 Kapitel 6: Pipeline-Verarbeitung

- 00:44:04 Serielle Befehlsabarbeitung

- 00:45:58 6.1 Pipeline-Verarbeitung

- 00:52:50 Pipelining »Fließband-Bearbeitung«

- 00:53:58 Wäsche-Pipelining

- 00:54:23 Beispiel

- 00:57:02 6.1 Pipeline-Verarbeitung

- 01:05:42 Pipelining

- 01:06:39 Einfache fünfstellige Befehlspipeline

- 01:10:26 Definitionen

- 01:10:37 6.2 Zerlegung in Pipeline-Stufen und Pipeline-Register

- 01:17:10 Definitionen

- 01:17:13 Einfache fünfstellige Befehlspipeline

- 01:19:58 Leistungssteigerung durch Pipelining

- 01:28:36 Durchsatz

Laufzeit (hh:mm:ss)

01:30:55

Serie

Rechnerorganisation, SS 2015, Vorlesungen

Publiziert am

25.11.2015

Fachgebiet

Lizenz

Aufrufe

168

| Auflösung | 1280 x 720 Pixel |

| Seitenverhältnis | 16:9 |

| Audiobitrate | 93839 bps |

| Audio Kanäle | 2 |

| Audio Codec | aac |

| Audio Abtastrate | 48000 Hz |

| Gesamtbitrate | 899840 bps |

| Farbraum | yuv420p |

| Container | mov,mp4,m4a,3gp,3g2,mj2 |

| Medientyp | video/mp4 |

| Dauer | 5455 s |

| Dateiname | DIVA-2015-856_hd.mp4 |

| Dateigröße | 4.096 byte |

| Bildwiederholfrequenz | 25 |

| Videobitrate | 799890 bps |

| Video Codec | h264 |

Mediathek-URL

Embed-Code

Rechnerorganisation, SS 2015, Vorlesungen

Folgen 1-25

von 25