FAQ

Audio-/Videodatei publizieren

Rechnerorganisation, Vorlesung, WS 2016/17, 28.11.2016, 11

Autor

Herausgeber

Beteiligtes Institut

Institut für Technische Informatik (ITEC)

Fakultät für Informatik (INFORMATIK)

Genre

Beschreibung

- 0:00:00 Starten

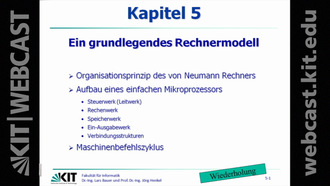

- 0:00:09 Fortsetzung Kapitel 5 - Ein grundlegendes Rechnermodell

- 0:00:55 Wiederholung: 5.1 Organisationsprinzip des von Neumann Rechners

- 0:01:41 Wiederholung: 5.2 Aufbau eines einfachen μP

- 0:04:36 Wiederholung: Aufbau eines einfachen μP - Registersatz

- 0:04:54 Wiederholung: Der (Laufzeit-)Stack ""Kellerspeicher""

- 0:06:09 Wiederholung: Hardware-Unterstützung des Stacks

- 0:06:42 Verwaltung des Stackregisters

- 0:11:34 Aufbau eines einfachen μP - Adresssatz / Systembusschnittstelle / Interne Busse

- 0:11:58 5.2.4 Adresswerk

- 0:12:53 Aufbau eines einfachen Adresswerks

- 0:15:33 Funktionsweise

- 0:16:52 Das Adresswerk

- 0:17:13 5.2.5 Systembus-Schnittstelle

- 0:18:37 5.2.6 Interne Busse

- 0:19:33 Weitere Funktionseinheiten

- 0:19:58 Pentium 4 Prozessor-Architektur

- 0:25:12 Kapitel 6 - Pipeline-Verarbeitung

- 0:26:05 Serielle Befehlsabarbeitung

- 0:27:22 6.1 Pipeline-Verarbeitung

- 0:28:50 Pipelining ""Fließband-Bearbeitung""

- 0:30:54 Wäsche-Pipelining

- 0:33:12 Pipeline-Verarbeitung

- 0:34:53 Einfache fünfstufige Befehlspipeline

- 0:36:55 Definitionen

- 0:38:15 6.2 Zerlegung in Pipeline-Stufen und Pipeline-Register

- 0:40:55 Definitionen

- 0:45:07 Leistungssteigerung durch Pipelining

- 0:50:14 Durchsatz

- 0:55:28 Befehlsabarbeitung und Datenpfade der MIPS-Befehle

- 0:55:55 Befehlsformate

- 0:56:22 6.3 Befehlsabarbeitung und Datenpfade der MIPS-Befehle

- 0:57:14 6.3 Befehlsabarbeitung und Datenpfade

- 1:02:06 6.3 Befehlsabarbeitung und Datenpfade - Lade- und Speicherbefehle (load and store)

- 1:06:19 6.3 Befehlsabarbeitung und Datenpfade - Verzweigungsbefehle

- 1:12:16 6.3 Befehlsabarbeitung und Datenpfade - Datenpfad für Lade-Speicherbefehle und Befehle vom R-Typ

- 1:15:50 Datenpfad für die MIPS-Architektur (1)

- 1:17:03 Erinnerung: MIPS-Befehlsformate

- 1:17:38 Datenpfad für die MIPS-Architektur (2)

- 1:24:02 Zustandsautomat

- 1:25:21 Steuersignale für den Datenpfad

- 1:26:15 6.4 Pipelining in MIPS-Architektur

Laufzeit (hh:mm:ss)

01:31:07

Serie

Rechnerorganisation, Vorlesung, WS 2016/17

Publiziert am

08.12.2016

Fachgebiet

Lizenz

Aufrufe

315

| Auflösung | 1280 x 720 Pixel |

| Seitenverhältnis | 16:9 |

| Audiobitrate | 103460 bps |

| Audio Kanäle | 2 |

| Audio Codec | aac |

| Audio Abtastrate | 48000 Hz |

| Gesamtbitrate | 908546 bps |

| Farbraum | yuv420p |

| Container | mov,mp4,m4a,3gp,3g2,mj2 |

| Medientyp | video/mp4 |

| Dauer | 5467 s |

| Dateiname | DIVA-2016-792_hd.mp4 |

| Dateigröße | 4.096 byte |

| Bildwiederholfrequenz | 25 |

| Videobitrate | 798988 bps |

| Video Codec | h264 |

Mediathek-URL

Embed-Code

Rechnerorganisation, Vorlesung, WS 2016/17

Folgen 1-27

von 27