FAQ

Audio-/Videodatei publizieren

19: Digitaltechnik und Entwurfsverfahren, Vorlesung, SS 2018, 17.07.2018

Autor

Herausgeber

Beteiligtes Institut

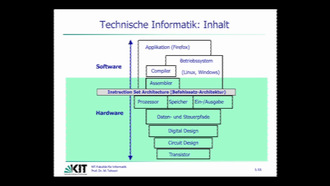

Institut für Technische Informatik (ITEC)

Genre

Beschreibung

- 0:00:00 Starten

- 0:01:05 Serienaddierer

- 0:03:32 Kapitel 4.4.1: Aufstellen des Automatengraphen

- 0:04:41 Blockschaltbild des Serienaddierers

- 0:05:33 Automatengraph

- 0:08:09 Kapitel 4.4.2: Aufstellen der Automatentafel

- 0:08:53 Stabile/Instabile Zustände

- 0:10:20 Kapitel 4.4.3: Wahl der Zustandskodierung

- 0:10:28 Wahl der Zustandskodierung

- 0:12:25 Kapitel 4.4.4: Ausgabe- und Übergangsschaltnetze

- 0:12:42 Kodierte Ablauftabelle

- 0:17:37 Wahl des Flipflops-Typs

- 0:18:04 Ansteuerung des Flipflops

- 0:20:58 Kapitel 4.5: Spezielle Schaltwerksbausteine

- 0:22:56 Kapitel 4.5.1: Register

- 0:24:04 4-Bit-Register aus D-Flipflops mit Freigabesignal

- 0:29:04 Kapitel 4.5.2: Schieberegister

- 0:35:37 Schieberregister mit parallelen Eingängen

- 0:37:34 Schieberegister: Division/Multiplikation mit 2

- 0:39:32 Schieberegister: Umlaufspeicher/Ringzähler

- 0:43:00 Kapitel 4.5.3: Zähler

- 0:43:10 Aufgaben in digitalen Systemen

- 0:52:29 Asynchrone Zähler (Ripple Counter)

- 0:57:23 Partitionieren

- 0:58:16 Kapitel 4.5.4: Programmierbare Bausteine

- 0:58:58 NAND-Gatter im Gate-Array-Entwurfsstil

- 1:02:52 Aufbau eines MPGA (ASIC)

- 1:04:13 Prinzipieller Aufbau eines FPGAs

- 1:13:43 Entwurf mit FPGAs

Laufzeit (hh:mm:ss)

01:17:02

Serie

Digitaltechnik und Entwurfsverfahren, Vorlesung, SS 2018

Publiziert am

19.07.2018

Fachgebiet

Lizenz

Aufrufe

23

| Auflösung | 1280 x 720 Pixel |

| Seitenverhältnis | 16:9 |

| Audiobitrate | 128000 bps |

| Audio Kanäle | 2 |

| Audio Codec | aac |

| Audio Abtastrate | 48000 Hz |

| Gesamtbitrate | 934096 bps |

| Farbraum | yuv420p |

| Container | mov,mp4,m4a,3gp,3g2,mj2 |

| Medientyp | video/mp4 |

| Dauer | 4622 s |

| Dateiname | DIVA-2018-578_hd.mp4 |

| Dateigröße | 539.625.078 byte |

| Bildwiederholfrequenz | 25 |

| Videobitrate | 799998 bps |

| Video Codec | h264 |

Embed-Code

Digitaltechnik und Entwurfsverfahren, Vorlesung, SS 2018

Folgen 1-20

von 20