FAQ

Audio-/Videodatei publizieren

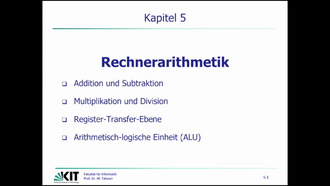

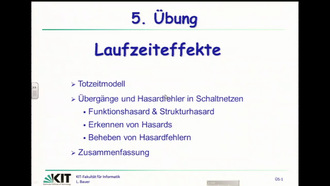

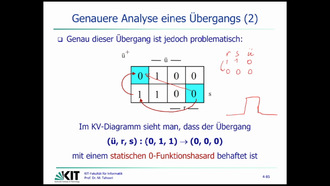

20: Digitaltechnik und Entwurfsverfahren, Vorlesung, SS 2018, 19.07.2018

Autor

Herausgeber

Beteiligtes Institut

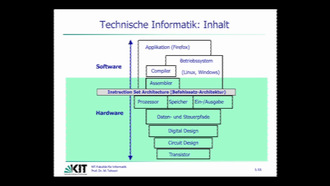

Institut für Technische Informatik (ITEC)

Genre

Beschreibung

- 0:00:00 Start

- 0:00:11 Rechnerarithmetik

- 0:01:51 Addition und Subtraktion

- 0:02:09 Addition von Festkomma-Dualzahlen

- 0:03:06 Addition von Gleitkommazahlen

- 0:03:41 Voll- und Halbaddierer

- 0:03:55 Halbaddierer

- 0:05:29 Volladdierer

- 0:10:04 Schaltnetz und Schaltsymbol

- 0:11:01 Serielle Addition

- 0:12:40 Carry-Ripple-Addierer

- 0:12:50 Addieren zweier Dualzahlen mit mehreren Stellen

- 0:13:18 Schaltbild: n-Bit Carry-ripple Addierer

- 0:15:44 Probleme

- 0:16:36 Berechnung der Überträge aus den Eingangsvariablen

- 0:18:10 Schaltbild: 3-Bit-Carry-lookahead-Addierer

- 0:19:32 Anmerkungen

- 0:20:19 Kaskadierung zweier 4-Bit Carry-lookahead-Addierer

- 0:20:54 BCD-Addierer

- 0:21:02 BCD Code

- 0:21:59 Beispiel

- 0:22:25 BCd Addition

- 0:23:53 Beispiel

- 0:26:28 Bestandteile BCD-Addierer

- 0:26:57 Fuktionstabelle für die BCD-Addition

- 0:27:03 Herleitung BCD-Addierer

- 0:27:18 BCD-Addierer für eine Tetrade

- 0:28:24 Subtraktion

- 0:28:37 Subtraktion durch Addition des Zweierkomplements

- 0:29:59 Subtraktion von Zweierkomplimentzahlen

- 0:30:36 Sonderfall 1

- 0:31:44 Beispiel für Sonderfall 1

- 0:32:50 Sonderfall 2

- 0:33:21 Beispiel für Sonderfall 2

- 0:34:10 Sonderfall 3

- 0:34:34 Beispiel für Sonderfall 3

- 0:34:38 Multiplikation und Division

- 0:35:03 Einleitung

- 0:35:54 Möglichkeiten

- 0:36:31 Multiplikation von Gleitkommazahlen

- 0:38:17 Parallele und serielle Multiplikation

- 0:38:26 Papier und Bleistift Methode

- 0:40:28 Vorzeichnen-Betrag-Zahlen

- 0:41:01 Partial Product Sum (PPS)-Methode

- 0:44:32 Beispiel

- 0:46:16 Implementierung der PPS-Methode

- 0:46:52 Datenfluss des seriellen Multiplizierers

- 0:49:35 Anmerkungen

- 0:50:52 Parallele Multiplikation

- 0:52:38 UND-Matrix: 3-Bit Parallelmultiplizierer

- 0:53:55 Division

- 0:54:07 Einleitung

- 0:55:07 Manuelle Division

- 0:56:08 Maschinelle Division

- 0:56:54 Durchführung der Subtraktion

- 0:57:29 Beispiel

- 0:59:21 Bemerkungen

- 1:00:04 Division

- 1:00:38 Blockschaltbild für sequentiellen Dividerer

- 1:01:14 Funktionsweise

- 1:02:03 Vorzeichenbehaftete Zahlen

- 1:02:45 Pentium Bug 1994

- 1:06:28 Arithmetisch-logische Einheit

- 1:06:50 Einleitung

- 1:07:19 Interner Aufbau eines einfachen mp

- 1:10:41 Rechenwerk

- 1:11:39 Schema einer einfachen ALU

- 1:12:48 Ein- und Ausgänge der ALU

- 1:13:47 Zusammenfassung von TI

Laufzeit (hh:mm:ss)

01:16:29

Serie

Digitaltechnik und Entwurfsverfahren, Vorlesung, SS 2018

Publiziert am

20.07.2018

Fachgebiet

Lizenz

Aufrufe

43

| Auflösung | 1280 x 720 Pixel |

| Seitenverhältnis | 16:9 |

| Audiobitrate | 128000 bps |

| Audio Kanäle | 2 |

| Audio Codec | aac |

| Audio Abtastrate | 48000 Hz |

| Gesamtbitrate | 889217 bps |

| Farbraum | yuv420p |

| Container | mov,mp4,m4a,3gp,3g2,mj2 |

| Medientyp | video/mp4 |

| Dauer | 4589 s |

| Dateiname | DIVA-2018-587_hd.mp4 |

| Dateigröße | 510.093.180 byte |

| Bildwiederholfrequenz | 25 |

| Videobitrate | 755113 bps |

| Video Codec | h264 |

Embed-Code

Digitaltechnik und Entwurfsverfahren, Vorlesung, SS 2018

Folgen 1-20

von 20