FAQ

Audio-/Videodatei publizieren

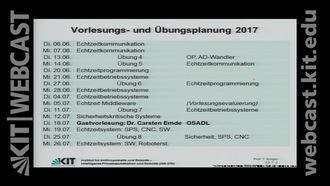

06: Echtzeitsysteme, Vorlesung, SS 2017, 10.05.2017

Autor

Herausgeber

Beteiligtes Institut

Institut für Anthropomatik und Robotik (IAR)

Genre

Beschreibung

- 0:00:00 Starten

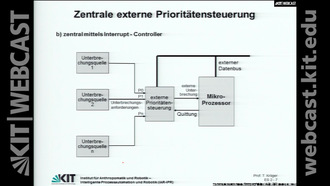

- 0:00:12 Zentrale externe Prioritätensteuerung

- 0:01:47 Prinzipieller Aufbau eines Mikrocontrollers

- 0:02:41 Prinzipieller Aufbau einer Zähler-/Zeitgebereinheit

- 0:04:15 Prinzipieller Aufbau eines Watchdog

- 0:06:02 Serielle und parallele Ein-/Ausgabekanäle

- 0:10:39 Jitter: Zeitliche Fluktuationen in digitalen Signalen

- 0:19:36 Aufbau einer Echtzeit-Ausgabeeinheit

- 0:20:57 Jitterfreie Echtzeit-Ausgabeeinheit

- 0:23:52 AD-/DA-Wandler zwischen digitalen und analogen Signalen

- 0:25:25 DMA

- 0:26:40 Grundlage Aufbau eines Signalprozessors

- 0:30:49 Signalprozessor-Befehlsworte

- 0:33:25 Eingebettete Echtzeit-Systeme

- 0:39:38 PC-basierte Echtzeitsysteme

- 0:48:16 Aufbau eines PC-Motherboards

- 0:48:54 Layout-Skizze eines Motherboards

- 0:50:41 Systembusse für die Vernetzung innerhalb von PC-basierten Systemen

- 0:51:44 Beispiele eines prozessorabhängigen Systembusses

- 0:54:17 Gepufferter, entkoppelter Bus

- 0:56:00 Synchroner Systembus

- 0:58:48 Asynchroner Systembus

- 1:00:00 Merkmale Systembusse

- 1:03:13 Buszuteilung

- 1:06:39 Mehrere Busmaster

- 1:07:25 Externer Bus - Arbiter

- 1:08:34 Zentraler Bus - Arbiter

- 1:09:42 Dezentraler Bus - Arbiter

- 1:11:51 Identifikationsbus

- 1:14:51 Echtzeitaspekte von Systembussen

- 1:20:06 Beispiel 1: Der PCI - Bus

Laufzeit (hh:mm:ss)

01:20:33

Serie

Echtzeitsysteme, Vorlesung, SS 2017

Publiziert am

18.05.2017

Fachgebiet

Lizenz

Aufrufe

19

| Auflösung | 1280 x 720 Pixel |

| Seitenverhältnis | 16:9 |

| Audiobitrate | 91218 bps |

| Audio Kanäle | 2 |

| Audio Codec | aac |

| Audio Abtastrate | 48000 Hz |

| Gesamtbitrate | 896963 bps |

| Farbraum | yuv420p |

| Container | mov,mp4,m4a,3gp,3g2,mj2 |

| Medientyp | video/mp4 |

| Dauer | 4833 s |

| Dateiname | DIVA-2017-242_hd.mp4 |

| Dateigröße | 4.096 byte |

| Bildwiederholfrequenz | 25 |

| Videobitrate | 799649 bps |

| Video Codec | h264 |

Embed-Code

Echtzeitsysteme, Vorlesung, SS 2017

Folgen 1-28

von 28